|

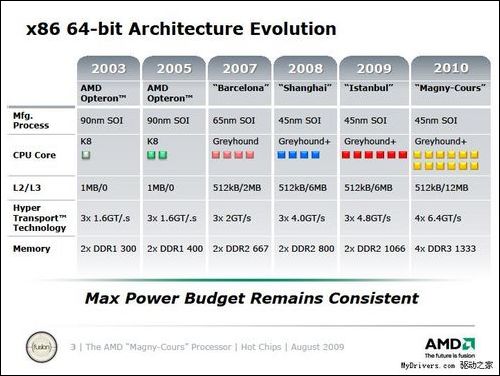

1回顶部 在当地时间8月23日的斯坦福大学Hot Chips 21大会上,Intel、AMD纷纷介绍了各自的高端多路服务器处理器,前者是八核心“Nehalem-EX/Beckton”,后者则是十二核心“Magny-Cours”(马尼库尔)。 AMD的十二核心马尔库尼和四核心上海、六核心伊斯坦布尔一样基于K10 Greyhound+增强型架构,由GlobalFoundries采用45nm SOI工艺制造,每个核心搭配512KB二级缓存,每六个核心共享6MB三级缓存、总计12MB,整个处理器拥有四条速度为6.4GT/s的HT 3.0总线,以及两个双通道DDR3-1333内存控制器。 简单地说,马尼库尔就是采用第二代直连架构DAC 2.0和第二代多芯片模块技术MCM 2.0、将两颗伊斯坦布尔芯片(DIE)封装在一块基片上得来的,AMD称它们为节点(NODE)。 AMD在整个系统中使用了多种不同形式的HyperTransport 3.0超传输总线连接:两个节点分别有一条x16 ncHT(非相关性超传输总线),其一用于二者之间的内部连接,其二用于和系统其它部分连接,用于输入输出(I/O);同时两个节点又都能向外提供一条x16 cHT(相关性超传输总线)和一条x8 cHT连接。 在双路系统中,两颗处理器的四个节点之间通过两条x16 cHT和两条x8 cHT进行交叉连接,对外是两条x16 ncHT I/O连接,系统内存总带宽85.6GB/s,XFIRE带宽71.7GB/s。(XFIRE带宽:在HT连接是唯一瓶颈的情况下的最大可用一致性内存带宽) 2回顶部 四路系统的互连又完全不同了:x16 cHT连接被拆分成两条x8 cHT,这样每个节点就有三条x8 cHT,可分别连接其它三颗处理器中的一个节点,全部十二个节点因此分成两个小组,各自通过六条x8 cHT进行交叉互连,对外则有四条x16 ncHT I/O连接,系统内存总带宽170.4GB/s,XFIRE带宽143.4GB/s。 另外与巴塞罗那/上海相比,伊斯坦布尔/马尼库尔还引入了一项关键技术“HT Assist”(Probe Filter)。这是一种稀疏目录缓存,占用1MB三级缓存空间,与内存控制器协作,追踪系统里的所有行缓存,在双路、四路系统中能消除大多数探测广播,效果就是降低本地DRAM延迟和队列,并提高系统带宽。 AMD表示,这种双芯片封装形式能有效提高产品良率、降低生产成本、保证供应稳定性,同时热设计功耗会和伊斯坦布尔保持在同等水平。 马尔库尼将于2010年年初正式发布,命名为Opteron 6000系列,接口改为Socket G34(代表第三代四通道DDR3内存控制器),面向双路、四路领域。 同时还会有新款六核心“Lisbon”(里斯本),采用Socket C32接口(第三代双通道DDR3),命名为Opteron 4000系列,主要用于单路和双路领域。

|

正在阅读:AMD十二核心皓龙处理器马尔库尼技术详解AMD十二核心皓龙处理器马尔库尼技术详解

2009-08-26 13:57

出处:驱动之家

责任编辑:wenzhicheng

海信(Hisense)7公斤滚筒洗衣机全自动 超薄嵌入 小型家用 除菌洗 冷水护色洗HG70DA10以旧换新

949元

海信(Hisense)7公斤滚筒洗衣机全自动 超薄嵌入 小型家用 除菌洗 冷水护色洗HG70DA10以旧换新

949元 西门子(SIEMENS)274升大容量家用三门冰箱 混冷无霜 零度保鲜 独立三循环 玻璃面板 KG28US221C

4899元

西门子(SIEMENS)274升大容量家用三门冰箱 混冷无霜 零度保鲜 独立三循环 玻璃面板 KG28US221C

4899元 美的(Midea) 微波炉家用小型旋转加热20L 智能蒸煮菜单 杀菌功能 M1-L213C

509元

美的(Midea) 微波炉家用小型旋转加热20L 智能蒸煮菜单 杀菌功能 M1-L213C

509元 苏泊尔(SUPOR)电饭煲4L电饭锅电饭锅多功能一体家用蓝钻圆厚釜4-5人可做锅巴饭煲仔饭智能预约蒸米饭1-8人 SF40FC875 4升预约定时

329元

苏泊尔(SUPOR)电饭煲4L电饭锅电饭锅多功能一体家用蓝钻圆厚釜4-5人可做锅巴饭煲仔饭智能预约蒸米饭1-8人 SF40FC875 4升预约定时

329元 品胜 充电宝65W大功率30000毫安大容量PD20W快充户外移动电源适用笔记本电脑苹果15华为P70小米

259元

品胜 充电宝65W大功率30000毫安大容量PD20W快充户外移动电源适用笔记本电脑苹果15华为P70小米

259元 绿联何同学推荐65W氮化镓充电器套装多口Type-C快充头适用pd20W苹果15三星手机macbookPro笔记本电脑线

129元

绿联何同学推荐65W氮化镓充电器套装多口Type-C快充头适用pd20W苹果15三星手机macbookPro笔记本电脑线

129元 KZ Castor双子座有线耳机入耳式双单元哈曼曲线发烧HiFi耳返耳麦

88元

KZ Castor双子座有线耳机入耳式双单元哈曼曲线发烧HiFi耳返耳麦

88元 格兰仕(Galanz)电烤箱 家用烤箱 40L大容量 上下独立控温 多层烘培烤箱炉灯多功能 K42 经典黑 40L 黑色

459元

格兰仕(Galanz)电烤箱 家用烤箱 40L大容量 上下独立控温 多层烘培烤箱炉灯多功能 K42 经典黑 40L 黑色

459元 美的(Midea)中药锅煎药壶 智能全自动陶电砂锅炖药锅煲 煎药机器 养生熬药壶 大容量分体式 【4L容量】长效预约JYC4002

299元

美的(Midea)中药锅煎药壶 智能全自动陶电砂锅炖药锅煲 煎药机器 养生熬药壶 大容量分体式 【4L容量】长效预约JYC4002

299元 美的(Midea)电压力锅 高压锅家用5L双胆鲜汤深胆煮汤锅 智能多功能电饭煲 智能预约焖香饭智能 【5L高压浓香款】7段调压 多重口感 50Q3-FS

299元

美的(Midea)电压力锅 高压锅家用5L双胆鲜汤深胆煮汤锅 智能多功能电饭煲 智能预约焖香饭智能 【5L高压浓香款】7段调压 多重口感 50Q3-FS

299元 漫步者(EDIFIER)M25 一体式电脑音响 家用桌面台式机笔记本音箱 蓝牙5.3 黑色

129元

漫步者(EDIFIER)M25 一体式电脑音响 家用桌面台式机笔记本音箱 蓝牙5.3 黑色

129元 TCL电视 85英寸 120Hz 高色域 3+64GB 2.1声道音响 平板电视机 以旧换新 85英寸 官方标配

4799元

TCL电视 85英寸 120Hz 高色域 3+64GB 2.1声道音响 平板电视机 以旧换新 85英寸 官方标配

4799元